# A COMPARISON STUDY OF ESD PROTECTION FOR RFIC'S: PERFORMANCE vs. PARASITICS

# Haigang Feng, Ke Gong and Albert Z. Wang

Integrated Electronics Laboratory, Department. of Electrical & Computer Engineering Illinois Institute of Technology, 3301 S. Dearborn St., Chicago, IL 60616, email: awang@ece.iit.edu

# Abstract

This paper reports two advanced Electro-Static Discharging (ESD) protection structures suitable for RFIC's and a comparison study of influences of ESD parasitic capacitance (C<sub>ESD</sub>) on high-speed circuits. For a 4 Ghz ring-oscillator and a low-power high-speed Op-Amp circuits, it was observed that C<sub>ESD</sub> may corrupt high-speed performance significantly and new ESD structures can recover the corruption by 80%.

#### Introduction

On-chip ESD protection design becomes a major challenge in high frequency and very deep sub-micron (VDSM) IC design due to Si consumption and parasitic effects. For example, advanced RF IC chips require not only high ESD failure threshold voltage (ESDV>4KV), but also low parasitic capacitance and resistance that exist in all ESD units. Parasitic ESD capacitance (CESD) is normally ignored in designs. However, in high frequency design, e.g., RFIC's, CESD may be a killing factor. Traditional MOS-based ESD protection structures are not suitable to RFIC's because of its large size, hence high CESD. It is imperative to develop novel ESD protection devices for high-speed applications.

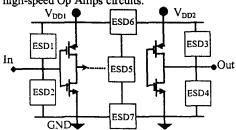

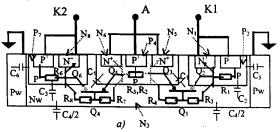

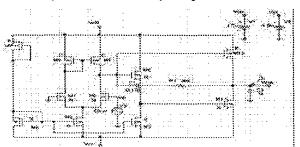

A complete full-chip ESD protection scheme is illustrated in Fig. 1, in which each bond-pad requires proper ESD protection devices. The ESD structures should be able to protect the chip against all ESD pulsing modes, i.e., I/O-to-V<sub>DD</sub> positively (PD) and negatively (ND) by ESD 1 & 3, I/O-to-ground (GND) positively (PS) and negatively (NS) by ESD 2 & 4, and from VDD-to-GND (DS) by ESD5[1] . In multi-supplies cases, ESD devices are also required between power buses (ESD 6 & 7). Clearly, if large ESD devices are used, one may encounter significant parasitic CESD, especially in high-pin-count design. In this paper, two compact ESD structures are reported. A comparison study of using conventional MOS ESD protection structures and the two new ESD designs will be discussed on the impacts of C<sub>ESD</sub> on circuit performance. The sample circuits used in this study are a GHz ring-oscillator clock generator and a lowpower, high-speed Op Amps circuits.

Fig. 1 A full-chip ESD protection scheme.

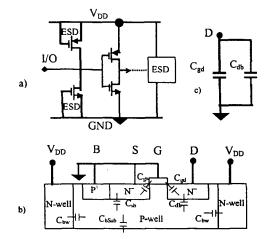

Fig. 2 ESDa: a) schematics, b) X-section, & c) C<sub>ESD</sub> model.

### **ESD Design and Measurements**

This work compares the conventional CMOS ESD structure (ESDa) with two new novel ESD structures (ESDb & ESDc)<sup>[2, 3]</sup> under the same ESDV = 4KV. The design was guided by an in-house developed mixed-mode ESD design-simulation methodology <sup>[4]</sup> for design prediction.

## A. ESDa: MOS ESD structures

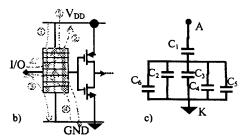

Fig. 2 illustrates the conventional MOS ESD protection structure. Normally, ground-gate NMOS and PMOS devices (GGNMOS & GGPMOS) are used to protect against ESD stresses at I/O pins w.r.t V<sub>DD</sub> and GND (PD. ND, PS, & NS)

Table I Data for ESD performance from simulation & measurement

| ESD<br>devices | Methods    | Triggering V <sub>tl</sub> (V) | Holding<br>V <sub>h</sub> (V)       | $R_{ON}(\Omega)$ |

|----------------|------------|--------------------------------|-------------------------------------|------------------|

| ESD a          | Simulation | 14.68                          | 6.92                                | ~1.9             |

|                | C-tracer   | 12.56                          | 6.48                                | -                |

|                | TLP        | 12.5                           | 6.5                                 | ~1.02            |

| ESD b          | Simulation | 23.32                          | 1.58                                | 0.73             |

|                | C-tracer   | 22.8                           | 1.55                                | -                |

|                | TLP        | 21.75                          | 2.96                                | 1.4              |

| ESD c          | Simulation | 20.82                          | 1.31                                | 0.5              |

|                | C-tracer   | 22.5                           | 1.5                                 |                  |

|                | TLP        | 21.66                          | 2.41                                | 1.37             |

|                | ESD pa     | pass level Simulated ESD dev   |                                     | ESD device       |

|                | Simulation | HBM Test                       | triggering time t <sub>1</sub> (nS) |                  |

| ESDa,200μ      | 4KV        | 4KV                            | 0.2                                 |                  |

| ESDb,50µ       | 4KV        | 4KV                            | 0.18                                |                  |

| ESDc,50µ       | 4KV        | 4KV                            | 0.16                                |                  |

as shown in Fig.2a. An extra ESD unit is needed for  $V_{DD}$ -to-GND protection.  $Fig.\ 2b$  is a typical NMOS cross-section that shows parasitic junction capacitance. Because the gates are grounded, only  $C_{gd}$  and  $C_{db}$  have effects as modeled by  $Fig.\ 2c$ . Both NMOS and PMOS ESD structures contribute to the overall parasitic capacitance,  $C_{ESD}$ . Multiple-finger MOS structure is used as usual. From ESD simulation, four 50 $\mu$ m-long NMOS fingers were needed to achieve ESDV of 4KV design goal. ESD measurements include quasi-DC tests by curve tracer (Tektronik 310), transient tests by a transmission-line-pulsing tester (Barth 4002), and standard HBM zapping tests (IMCS 10000). The ESD structure passed 4KV HBM stressing as designed. ESD data from simulation and measurements shows good match as shown in  $Table\ I$ . The extracted  $C_{ESD}$  data are listed in  $Table\ II$ .

Table II C<sub>ESD</sub> data (exclusive V<sub>DD</sub>-Gnd protection)

| For same ESDV=4KV     |             | ESDa | ESDb  | ESDc |

|-----------------------|-------------|------|-------|------|

| Parasitic             | Haif ESD,1x | 0.27 | 0.044 | 0.07 |

| C <sub>ESD</sub> (pF) | Full ESD,2x | 0.54 | 0.09  | 0.07 |

### B. ESDb: A Dual-Direction ESD Structure

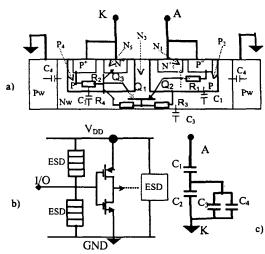

Ideally, an ESD protection unit should provide lowimpedance current shunting-channels formed by active devices in all ESD stressing modes (PD, ND, PS & NS). However, in the NMOS ESD structure, only one current discharging path is formed by a NPN device, with a reversebiased parasitic diode serving as 1-shunting path in the opposite direction. There are two shortcomings: first, the reverse-biased diode has high impedance that limits the ESDV level; second, it can not be used for  $V_{DD}$ >5V because  $10\% \Delta V_{DD}$  may turn on the diode accidentally. A new dualdirection ESD protection structure (ESDb) was designed to address this problem as illustrated in Fig. 3. Briefly, ESDb is a two-terminal (A & K), five-layer  $(N_1P_2N_3P_4N_5)$  structure consists of one lateral PNP transistor  $(Q_1=P_2N_3P_4)$ , two vertical NPN transistors  $(Q_2=N_1P_2N_3 \& Q_3=N_3P_4N_5)$  and four parasitic resistors,  $R_1$ ,  $R_2$ ,  $R_3$ , &  $R_4$ . The structure is connected to form two functional SCR units: unit  $l=Q_1, Q_2$ ,  $R_1 & R_3$  and unit  $2 = Q_1$ ,  $Q_3$ ,  $R_2 & R_4$  with A and K being the electrodes. In operation, when a positive ESD pulse appears at A (w.r.t. K), BC junction  $(N_3P_4)$  of  $Q_1$  is reverse biased to its breakdown and the generated holes are collected by the negative terminal K via  $P_4$ - $P^+$  layer. Since both the  $P_4$ - $P^+$ and  $N_5-N^+$  layers are connected to K,  $V_{BE}$   $(P_4N_5)$  of  $Q_3$ increases and eventually turns on  $Q_3$ . The SCR unit 1  $(P_2N_3P_4N_5)$  is therefore triggered off (at  $V_{11}$ ) and driven into deep snapback region (holding voltage  $V_h \leq 2V$ ). An active discharge path with negligible impedance RON is thereby formed to shunt the huge current surge and clamp the I/O pad voltage at a sufficient low level  $(V_h \le 2V)$ , thus protects ICs from being ESD-damaged. After the ESD pulse is over, the thyristor is quickly discharged and then turned off when the current decreases to below its holding current level. Similarly, the SCR unit 2  $(P_4N_3P_2N_1)$  operates during a negative ESD pulse event (K w.r.t. A). Hence this forms a

Fig. 3 ESDb: a new dual-direction ESD protection device.

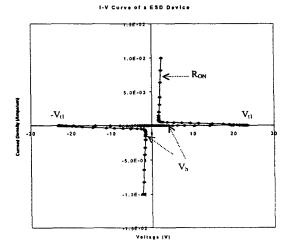

dual-direction ESD protection device. Symmetric operation is illustrated in Fig. 4. ESD data from simulation and measurements are listed in Table 1. A 50µm device passed HBM ESDV=4KV as designed and a 200µm device passed 14KV (test limit). Compared to the MOS ESDa, the ESDb features dual-polarity operation and small size. Therefore, ESDb has much lower C<sub>ESD</sub> as shown in Table 11, which greatly reduces the capacitive effects on the circuits. However, two ESDb's are still needed for each 1/O pin for 1/O-to-V<sub>DD</sub> and 1/O-to-Gnd, respectively. In addition, one extra ESD protection unit is needed for V<sub>DD</sub>-to-Gnd protection as is in the MOS ESD case. Hence sizable C<sub>ESD</sub> still exists, especially in high-pin-count cases.

C. ESDc: An All-Direction ESD Structure

To improve ESDb, a new all-direction ESD protection

Fig. 4 Simulated I-V curve of ESDb shows symmetry.

structure (ESDc) was designed. ESDc is a three-terminal (A,  $N_8$ ) as illustrated in Fig. 5a. It consists of six bipolar transistors and eight parasitic resistors, which are electrically connected to form two ESDb-type functional units. Unit I consists of  $Q_1 = P_2N_3P_4$ ,  $Q_2 = N_1P_2N_3$ ,  $Q_3 = N_3P_4N_5$ ,  $R_1$ ,  $R_2$ ,  $R_3$ & R<sub>4</sub>. Unit II has  $Q_4 = P_4N_3P_7$ ,  $Q_5 = N_6P_4N_3$ ,  $Q_6 = N_3P_7N_8$ , R<sub>5</sub>, R<sub>6</sub>, R<sub>7</sub> & R<sub>8</sub>. Q<sub>3</sub> and Q<sub>5</sub> share base and collector layers. R<sub>2</sub> and R<sub>5</sub> split the resistor of layer P<sub>4</sub>. A complete full-ESD protection scheme using ESDc is shown in Fig. 5b. Operation of ESDc is basically a dual-operation of ESDb units. Its three electrodes, A, K<sub>1</sub> & K<sub>2</sub>, are connected to 1/O pin, V<sub>DD</sub> and Gnd, respectively, on a chip. It is normally off. During ESD events, when ESD pulses appear at I/O pin w.r.t. to V<sub>DD</sub> or GND, the Unit 1 or Unit 11 will function exactly the same way as the ESDb device does to provide adequate ESD protection correspondingly as described in Section B. ESDc also operates symmetrically as shown by one measured 1-V curve in Fig. 6. Typical ESD data from simulation and tests are listed in Table 1. To achieve 4KV design goal, a 50µm device was needed, while a 200µm device passed over 14KV HBM stressing. The major advantages of the ESDc over the ESDb are the following. First, one ESDc device for each I/O pin can provide ESD protection against all four ESD pulsing modes: ND by path ①, PD by path ②, PS by path ③, and NS by path ④ as shown in Fig. 5b. Second, a similar ESDb-type SCR device exists between terminals K1 and K2, which forms a discharging path S to protect ESD surge from VDD to GND (DS). Therefore, one single ESDc-type device is enough to provide complete ESD protection for each I/O, including power buses. Third, it hence introduces much lower parasitic C<sub>ESD</sub> as shown in Table II. Another advantage of ESDc is that it is suitable for bondpad-oriented ESD design and is layout friendly. Overall, ESDb represents ~83% reduction in C<sub>ESD</sub> compared to CMOS ESDa, while ESDc further reduces  $C_{ESD}$  by ~ 22% over ESDb, therefore benefit circuits.

Fig. 5 ESDc: a)X-section; b) schematics & c) C<sub>ESD</sub> model.

### Influences of C<sub>ESD</sub> on High-Speed Circuits

Two circuits were designed to demonstrate the merits of the new ESD structures to high-frequency IC designs: a GHz ring-oscillator and a low-power, high-speed Op-Amp, using a 0.18µm 1.5V commercial CMOS technology.

### A. Improvement in Ring-Oscillator Clock Frequency

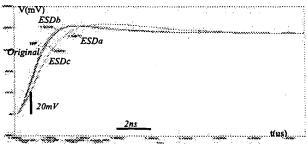

To demonstrate how seriously C<sub>ESD</sub> of ESDa units may degrade IC speed and how the new ESD structures, ESDb & ESDc, can alleviate this problem, a ring-oscillator circuit normally used to generate on-chip clock signals is designed. 15 stages were chosen for measurement concern and the targeting clock frequency was 4 Ghz. Since overall CESD effect in practical circuits varies according to 1/O pin counts, two ESD loading situations were considered in this work: a single-load scenario representing the least effect where only one I/O pin has ESD unit and a full-load scenario showing multi-pin ESD connection where ESD units were connected to each stage. Simulated signal waveforms are shown in Fig. 7 with delay time and frequency data listed in Tables III & IV. It is observed that C<sub>ESD</sub> of ESDa dramatically reduced the clock speed by 85% to 99% for single-load and full-load cases, respectively. However, the new ESD structures can recover the corruption significantly, 41% for ESDb and 62% for ESDc, respectively, in the single-load case.

Fig. 6 Measured I-V curve of ESDc device shows symmetry.

Table III Influences of C<sub>ESO</sub> on a 15-stage ring-oscillator circuit

| ESD type | Cap-load            | $C_{ESD}(pF)$ | t <sub>d</sub> (nS) | f(MHz) |

|----------|---------------------|---------------|---------------------|--------|

| None     | Original            | 0             | 0.211               | 4739   |

| ESDa     | Single load:        | 0.54          | 1.343               | 744.6  |

| ESDb     | 1xC <sub>cso</sub>  | 0.09          | 0.416               | 2402   |

| ESDc     |                     | 0.07          | 0.31                | 3226   |

| ESDa     | Full load:          | 0.54          | 23.91               | 41.82  |

| ESDb     | 15xC <sub>USD</sub> | 0.09          | 4.106               | 243.5  |

| ESDc     |                     | 0.07          | 3.291               | 303.9  |

Table IV Speed degradation w.r.t. original clock freq. due to C<sub>END</sub>

| L | ESD load | Original | ESDa        | ESDb           | ESDc    |

|---|----------|----------|-------------|----------------|---------|

|   | Single   | 0        | -84.92%     | <b>-49.31%</b> | -31.92% |

| ١ | ESD load | lmprove- | - +41.50% J |                |         |

| ١ |          | ment     | -           | +62.13%        | j       |

B. Improvement in Hi-Speed Op-Amp Performance

A low-power, high-speed, wide-swing Op Amp circuit,

designed for wireless communication applications, was used

to demonstrate the influences of parasitic  $C_{\rm ESD}$  on overall performance of a functional chip. The circuit topology, as shown in Fig. 8, features differential input, push-pull output stage for wide swing, level shift, capacitive compensation with nulling resistor for better stability, and global biasing for low-power. The critical performance data are listed in Table V that shows very low power consumption of 0.4 mW, high unity-gain and -3dB band-width of 126MHz and 40 KHz, wide swing of 0.96V measured at 80% small-signal gain, very high slew-rate of 115 mV/nS, and short settling time of 9 nS measured at 1% of the output.

Table V Op Amp critical specifications ( $C_L = 1 \text{ pF}$ )

| Technology   | 0.18um, 1.5V | Power supply (V)       | 1.5   |  |

|--------------|--------------|------------------------|-------|--|

| Gain (dB)    | 74.16        | Power cons. (mW)       | 0.41  |  |

| Phase margin | 61.3         | V-swing (V, 80%)       | 0.964 |  |

| fr (MHz)     | 126.3        | f.3dB (KHz)            | 40.6  |  |

| SR (mV/nS)   | 115.7        | Settling time (ns, 1%) | 9.38  |  |

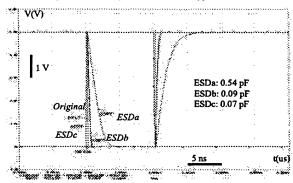

To evaluate the negative impacts of ESD on the Op Amp performance,  $C_{ESD}$  were connected to the output node for ESDa, ESDb and ESDc, respectively. Fig. 9 shows a sample small-signal step response for settling time measurements. The typical data are summarized in Table VI & VII. It is clear that the traditional CMOS ESD protection devices (ESDa) can substantially deteriorate performance of the high-speed Op Amp, i.e., over 30% deterioration in unitygain band-width, slew rate and settling time, all of which are critical in high-speed operation. Using the two advanced ESD structures (ESDb & c), the performance corruption may be recovered by  $60 \sim 80\%$  in this case.

Although this comparison study used two example circuits only, It is interesting to observe that, while higher ESD specifications is in demand, parasitic effects from the ESD protection units used may dramatically affect the core circuit being protected. Advanced low-parasitic ESD structures are important in RFIC designs and a designer must pay special attention to ESD side effects in high-speed designs.

Table VI Influences of  $C_{LSO}$  loads on an Op Amp at  $C_L = 1pF$

| ESD  | $C_{LSD}(pF)$ | fτ(MHz) | f.3dB(KHz) | SR(mV/ns) | tec(nS) |

|------|---------------|---------|------------|-----------|---------|

| None | 0             | 126.3   | 40.6       | 115.7     | 9.38    |

| ESDa | 0.54          | 86.2    | 37.6       | 80.6      | 13.09   |

| ESDb | 0.09          | 112.2   | 39.8       | 107.6     | 10.28   |

| ESDc | 0.07          | 118.6   | 39.8       | 109.3     | 10.13   |

Table VII Op Amp performance degradation due to CLSD loads

|             |          |               | radation due to C |          |  |

|-------------|----------|---------------|-------------------|----------|--|

| Parameters  | Original | ESDa          | ESDb              | ESDc     |  |

| ft (MHz)    | 126.3    | -31.75%       | -11.16%           | -6.1%    |  |

|             |          | <b>→</b> +64. | → +64.85% J       |          |  |

|             |          | )             | +80.86%           | <u> </u> |  |

| f.3d8 (KHz) | 40.6     | -7.4%         | -2%               | -2%      |  |

|             |          | → +83.        | .78% 3            |          |  |

|             |          | )             | +83.78%           | J        |  |

| Slew rate   | 115.7    | -30.34%       | -7%               | -5.5%    |  |

| (Vhis)      |          | <b>→</b> +76. | .93% J            |          |  |

|             |          | )             | +81.87%           | T T      |  |

| face        | 9.38     | -39.55%       | -9.59%            | -8%      |  |

| (nS, 1%)    |          | → +75.98% J   |                   |          |  |

|             |          | •             | +79.77%           | 7        |  |

#### Conclusions

In summary, a pair of novel, low-parasitic ESD protection structures for RFIC's was described. A comprehensive comparison study of possible ESD side-effects on the high-speed circuits protected was discussed. It was observed that ESD induced parasitic effects may degrade circuit performance significantly, while advanced low-parasitic ESD structures could substantially recover this type of circuit performance corruption. It is therefore imperative to use low-parasitic ESD protection and to include ESD related parasitic effects in RF and VDSM IC designs.

#### References

- (1) K. Narita, et al., IEEE Trans. on Elect. Dev., pp. 1124, 1997.

- (2) A. Wang, et al, U. S. Patent, Pending, January 1998.

- (3) A. Wang, U. S. Patent, Pending.

- (4) A. Wang, et al, In Proc of IEEE 5th ICSSICT, pp.509, 1998.

Fig. 7 In/Out waveforms of a ring oscillator with single C<sub>LSD</sub> load showing clock corruption from ESDa and recovery in using advanced ESD b &c.

Fig. 8 Schematics of a low-power, high-speed Op Amp circuit.

Fig. 9 Op Amp circuit: small-signal step response for settling time tests.